トランジスタ 特性 ばらつき

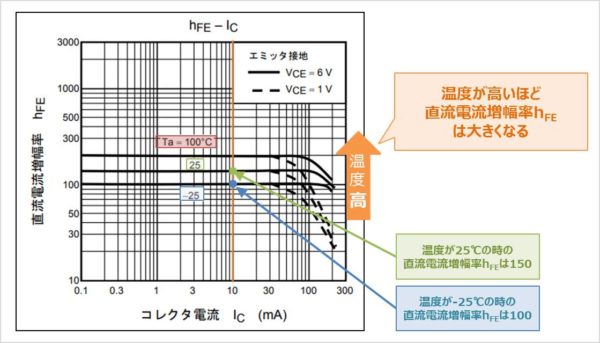

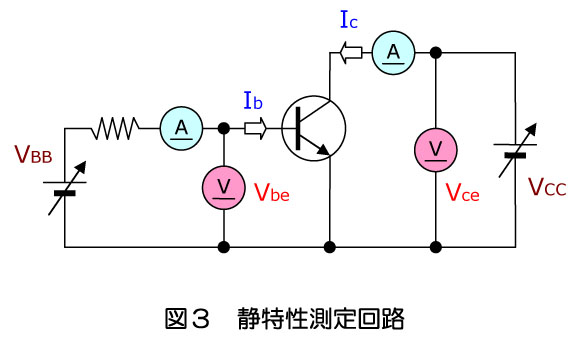

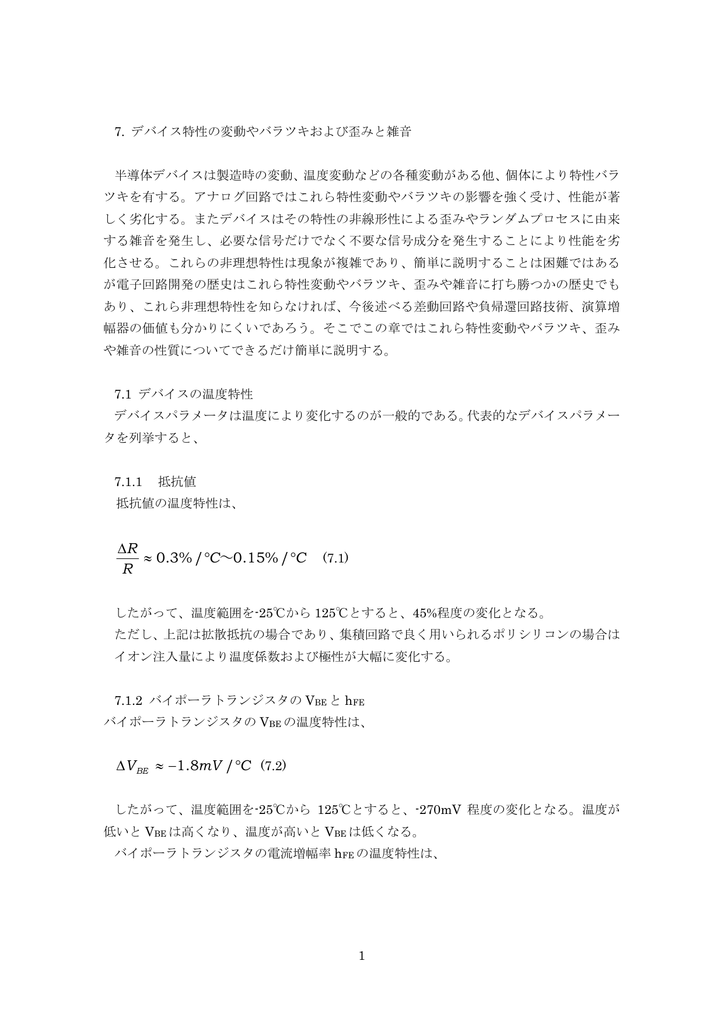

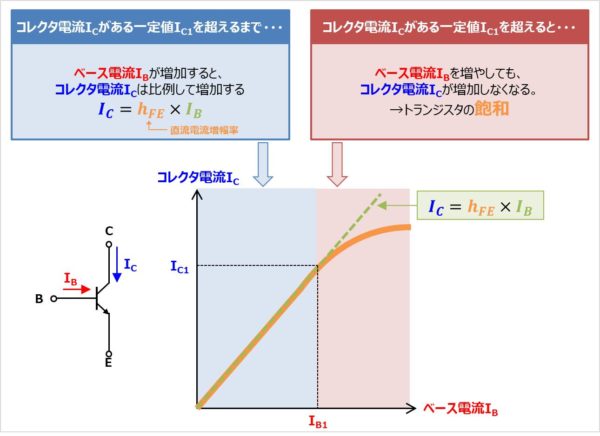

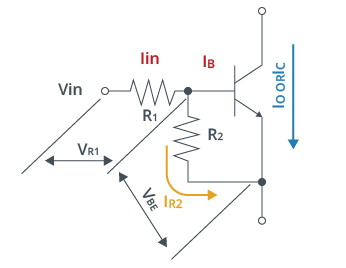

(4) VCE-VBE特性の傾きが電圧帰還率hreである。添え字rはreverse(逆)を表す。 h定数の値は,トランジスタの種類によって異なるばかりでなく,同一のトランジスタ でも,IC, VCE, 周辺温度によっても変わり,さらに製品のばらつきも見られる。.

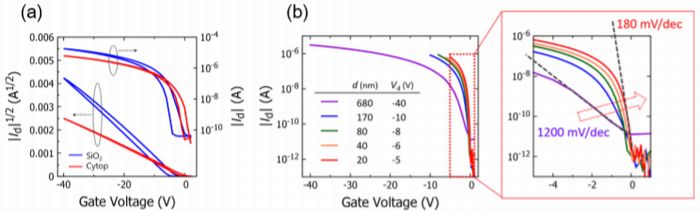

トランジスタ 特性 ばらつき. 4.1 cm2/Vs)を実現 概要 東京工業大学 科学技術創成研究院 未来産業技術研究所の飯野裕明准教授. 要点 液晶性有機半導体の特性を活用し従来に比べ2,000倍以上の成膜速度を達成 10 cm角基板にボトムゲートボトムコンタクト型トランジスタ250個を試作 素子間のばらつきの小さい高移動度(Ph-BTBT-10:. TFTの特性は,この電荷移動度μ,ドレイン電流Ids のOn/Off比,しきい値電圧Vt などにより表される。 また,これらの特性の時間変動も重要な.

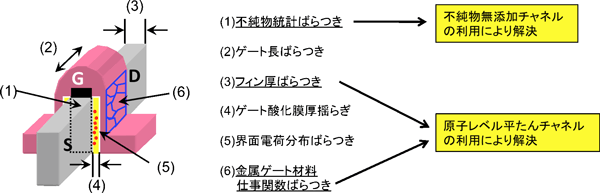

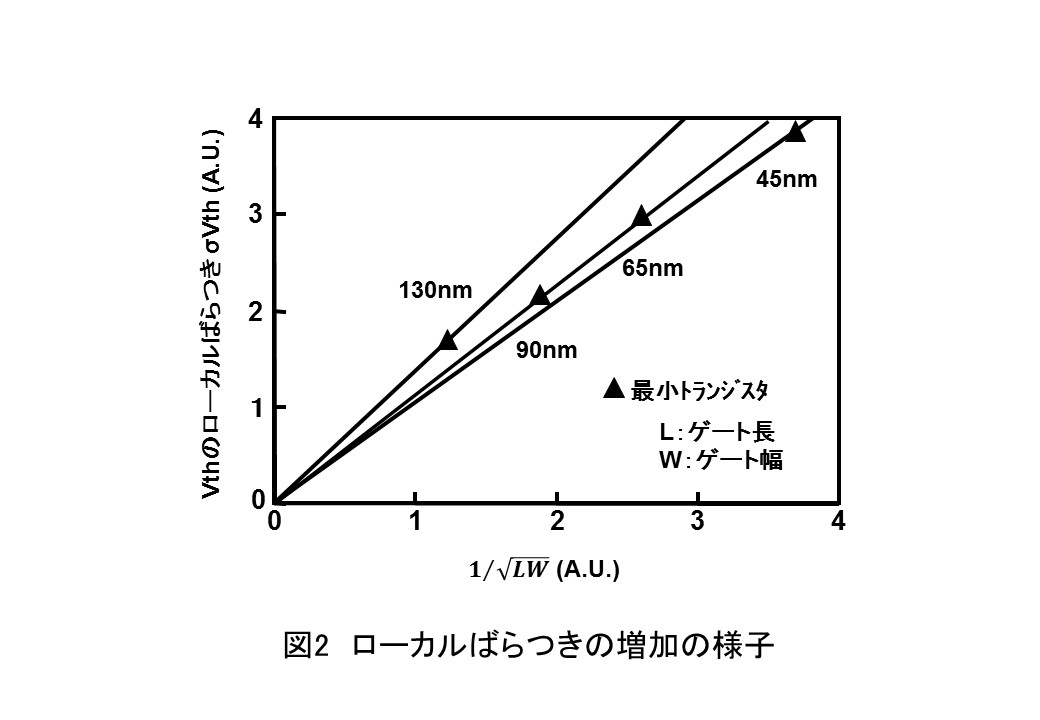

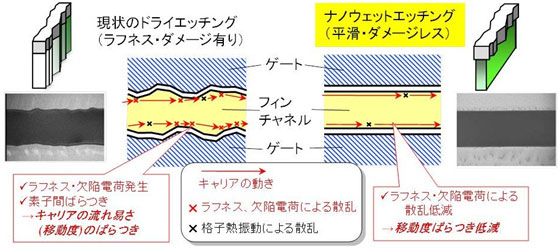

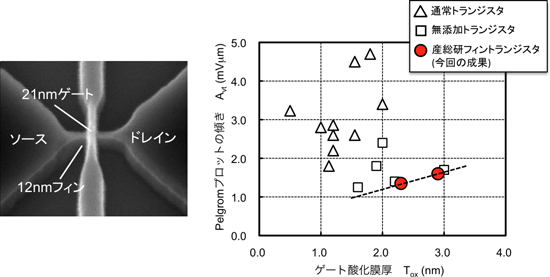

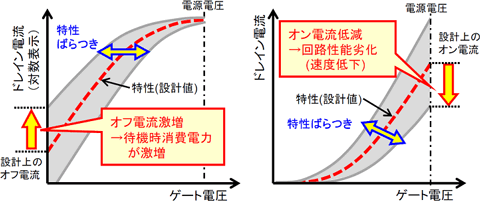

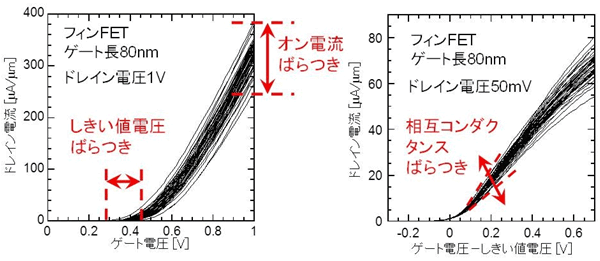

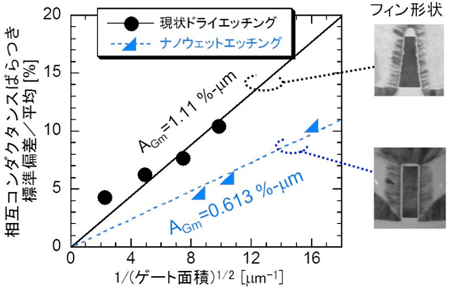

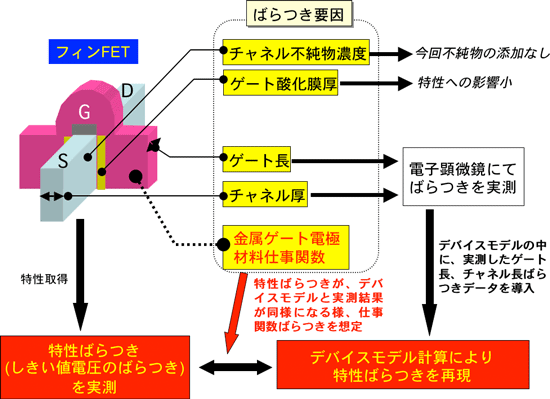

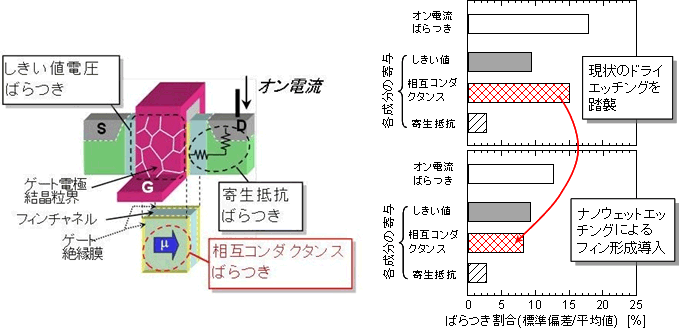

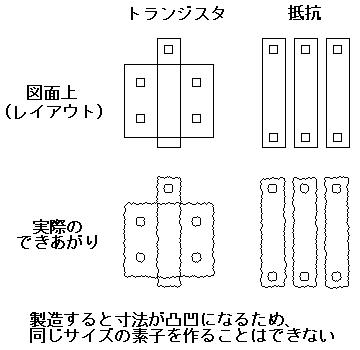

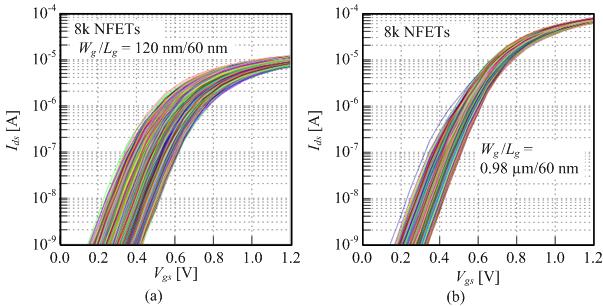

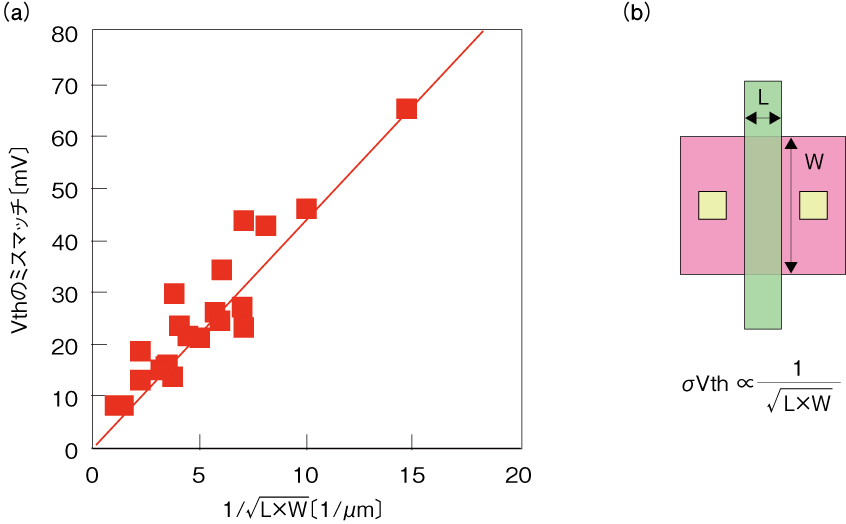

トランジスタのオン電流ばらつきの要因は、 しきい値電圧ばらつき、 寄生抵抗ばらつき、 相互コンダクタンスばらつきである。今回、各要因の寄与を詳細に解析することで、14 nm世代のフィンFETでは相互コンダクタンスばらつきがオン電流ばらつきの主要因となることを明らかにした。. Mosfetの特性についての豆知識ページです。 mosfetの寄生容量と温度特性について, mosfetのスイッチングとその温度特性について, mosfetのvgs(th)(しきい値)について説明しています。. ばらつき克服する設計技術 • ばらつきを観察する –0.35µm –0.18µm –0.13µm • ばらつきを再現する • ばらつきが回路特性に及ぼす影響 • 設計・回路技術でばらつきを克服する – 統計的特性解析技術 – 規則性の導入 – プログラマブルアレー構造.

2.4 量 産 性 (1) 均一な特性のものが容易に得られること.ト ラ ンジスタは特性のばらつきおよび変化が大きいから,特 に考慮を払わなければならない. トランジスタ特性ばらつきによるSRAM の不安定性に関する研究 A Study on SRAM Instability by Transistor Characteristics Variability 電気電子情報通信工学専攻 西野 佑 Tasuku Nishino 1. Ledについてのページです。 ledの注意が必要な特性を紹介します。 ledの光度,波長,順方向電圧などの特性は、周囲温度およびledの発熱を含めたチップの温度により、特性が変化します。 又、ledは製造段階で特性値の分布、いわゆるバラツキを持っています。.

まう現象をばらつきと呼ぶ)に大きく反映して回路特性を悪化させる. z差動増幅回路のオフセット zスタンバイ電流の増加 ゲート長L しきい値電圧V T P N+ N+ 設計ゲート長Lが小さい ほどトランジスタの特性 のばらつき大きくなる. ΔVT:大 L:短い L:長い. トランジスタのばらつきは、 図3 に示すように、「チップ 間ばらつき」と「チップ内ばらつき」に大きく分類できます。 「チップ間ばらつき」の影響は、チップ内部のクロックや 信号の遅延のチップ間差に現れます。「チップ内ばらつき」. デバイスの特性ばらつき • mosfetのvthばらつき, 温度変化の影響を表す式.

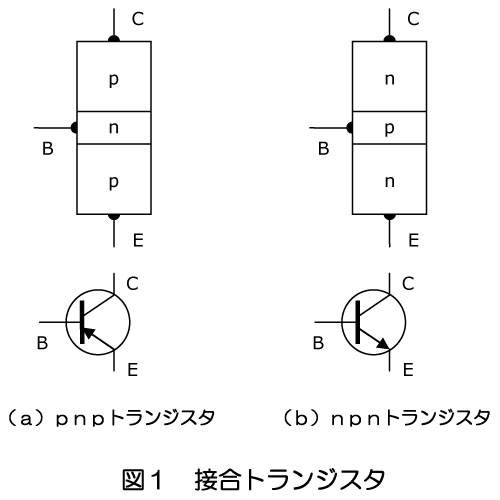

ものと、実際のチップの特性ばらつきを比較した結果は見たことがない。 18 SEMICON® Japan 07 モデリングの課題 トランジスタレベルでのモデル化は非常に困難な課題。. ばらつきの分類 一般にトランジスタの特性ばらつきは,空間分布の観 点から「グローバル」ばらつきと「ローカル」ばらつき に分類される.また,規則性の観点から「システマティッ ク」ばらつきと「ランダム」ばらつきに分類される.. (1) フォトカプラの特性 (2) 負荷を付けた特性 (3) 伝送用の特性 図 2.12 フォトトランジスタカプラの負荷特性例 vcc iin ic gnd tr.の場合 0 iin (ma) 5 10 ctr 小 i c (m a) ctr 大 cc 5 v 5 2.5 rl vcc iin ic gnd tr.の場合 0 iin (ma) 5 10 ctr 大 i c c (m a) ctr 小 cc rl 2 k:.

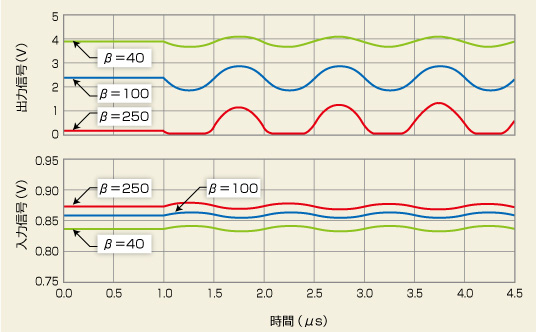

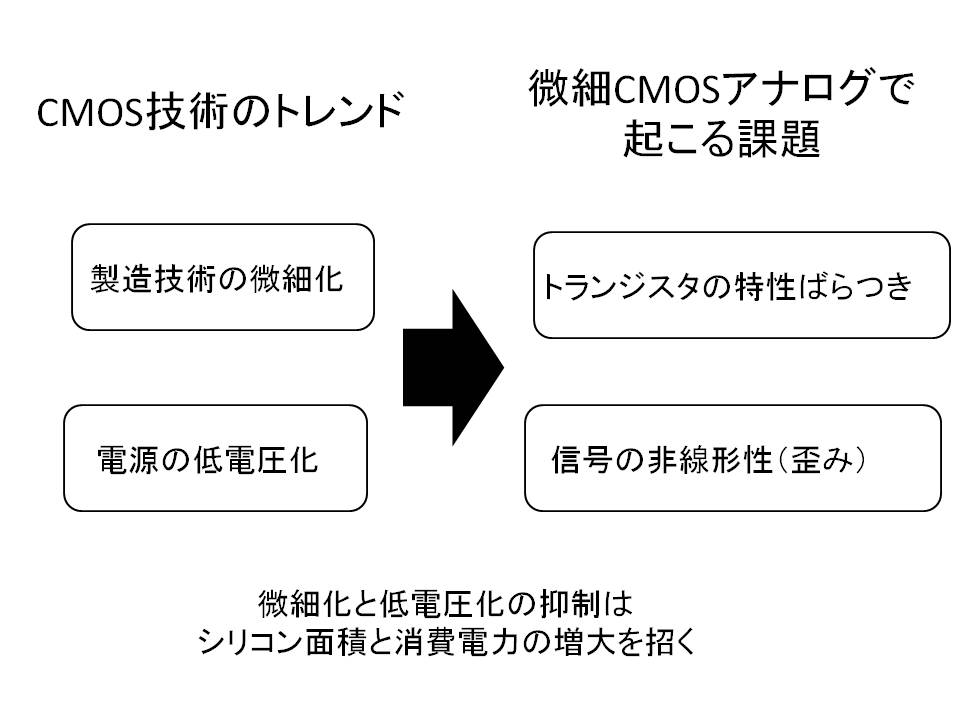

トランジスタの特性がばらつくと、アナログicの性能を劣化させてしまいます。 このばらつきが、微細化によって増大するのです。 だからといって、微細化しないトランジスタを内蔵したり、電源電圧を上げたりすると、シリコン面積の拡大(製造コストの. 第2 章 cmos インバータの動作 2.1 cmos インバータの基本動作 cmos インバータの回路を図2.1 で表す.nmos,pmos トランジスタを用いたソース接 地のプッシュプル回路であり,nmos,pmos 共に増幅作用がある. cmos インバータの動作は図2.1 を用いて次のように説明できる.入力電圧vin が上がれ. トランジスタの場合、なぜhパラメータを用いるのですか? 教えてください(>_<) 使いやすいからです.Zパラ、Yパラ、高周波ならSパラと、いろいろありますけど、相互に変換できますから、どれか一つが分かれば他は換算するだけです.ですから、状況に応じて使いやすいものを使えばよいわけ.

To provide a characteristics evaluation circuit and an evaluation method for a transistor, capable of analyzing dispersions in the characteristics of the plurality of transistors. トランジスタの特性 Vg (v) 0.2 0.4 0.6 0.8 1.0. ると、トランジスタが導通状態で流れる電流(オ ン電流)のばらつきなどの特性ばらつきが発生 します。17年以降に市場投入が想定されてい る14 nm世代トランジスタ技術では、その寸法 の小ささから素子間の特性ばらつきの問題が顕.

5 2.5 rl rl vcc iin ic gn tr. Mosトランジスタの耐ばらつきチャンネル分割に関する考察 劉 博 , 越智 敦 , 中武 繁寿 電子情報通信学会技術研究報告. Vol.43 No.5 情報処理学会論文誌 May 02 トランジスタ特性におけるチップ内ばらつきのモデル化手法 岡田健一† 小野寺 秀俊† 製造ばらつきを考慮した回路設計では,チップ間のばらつきのみならず,チップ内でのばらつきを.

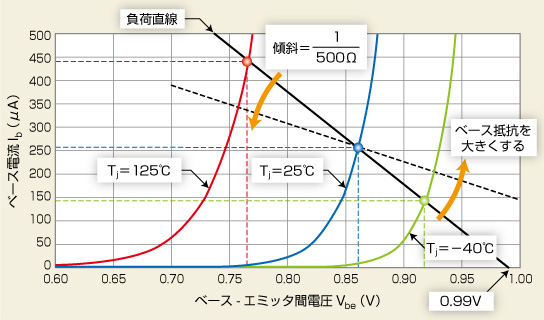

特性例として、ベースエミッタ間電圧 (vbe)とベース電流(ib)の関係を図4 に 示す。b-e 間はダイオードの順バイアスの 電圧電流特性と同じである。si トランジス タであれば、0.55v で急激にベース電流が 流れだす。 図4 典型的なi -vbe 特性例.

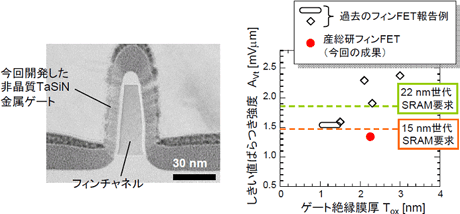

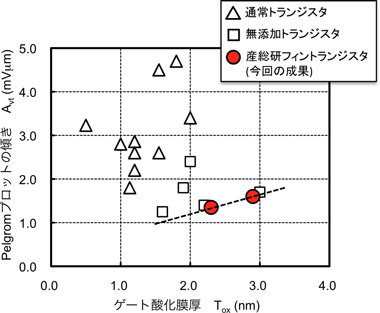

産総研 特性ばらつきが世界最小のフィンfetを実現

1998 号 定電流回路 Astamuse

Gpuを用いてmosトランジスタの性能限界を予測 修士2年 鈴木氏 半導体関連国際会議 iedm で研究発表 早稲田大学

トランジスタ 特性 ばらつき のギャラリー

Fffworks Fuzzface概論1 ゲルマtrの特性

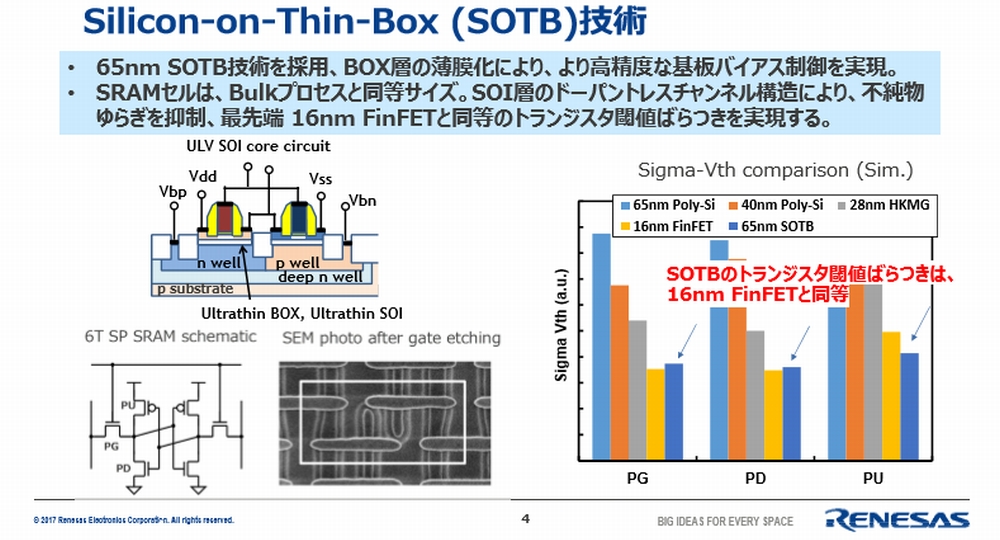

ルネサス 65nmsotbで低消費 高速の内蔵sram 1 2 Ee Times Japan

高速メモリ回路動作シミュレーションの世界最高クラス技術を開発 Nedo

パワーmosfetの実践活用法

第7回 エミッタ接地回路の温度対策 2 2 Ee Times Japan

Waseda Repo Nii Ac Jp Action Repository Uri Item Id File Id File No 3

トランジスタの増幅回路について Okwave

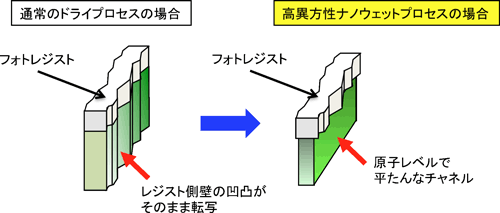

産総研 特性ばらつきが小さい22 Nm世代フィントランジスタを作製

2

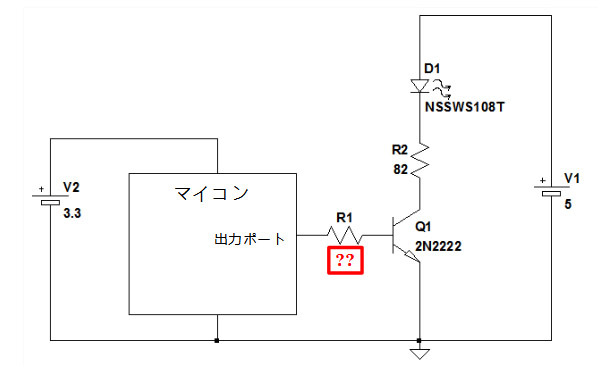

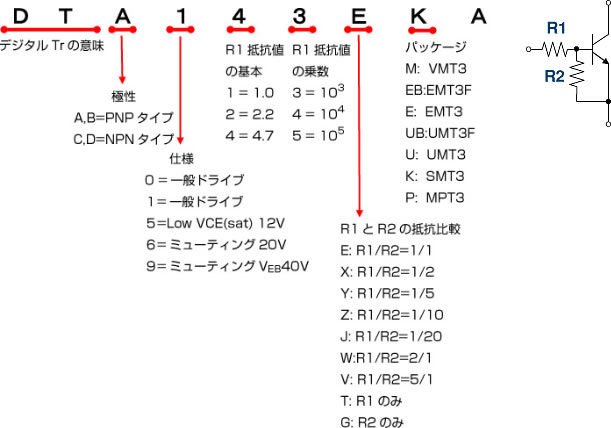

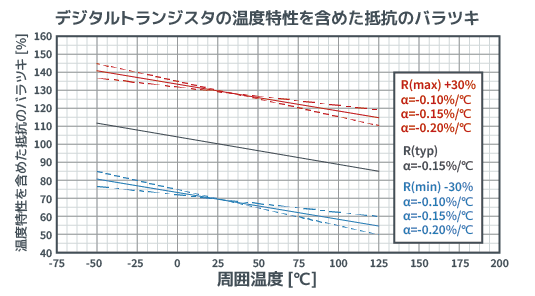

デジタルトランジスタ デジトラ の原理 トランジスタとは エレクトロニクス豆知識 ローム株式会社 Rohm Semiconductor

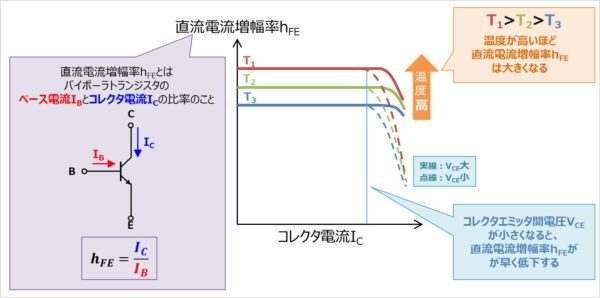

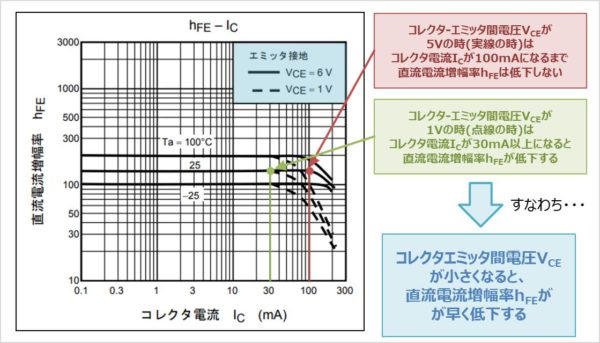

バイポーラトランジスタの Hfe Ic特性 について

2

バイポーラトランジスタの Hfe Ic特性 について

産総研 特性ばらつきが小さい22 Nm世代フィントランジスタを作製

情報技術の心臓部として活躍するlsi その設計課題に挑戦 研究室voice 大阪工業大学

アナログの基礎の基礎 トランジスタ編 5 バイポーラトランジスタ Venetor Sound

ケイレックス テクノロジー 半導体ソリューションサービス 統計的データ分析 モデル化

バイポーラトランジスタの Hfe Ic特性 について

Http Www Nedo Go Jp Content Pdf

Www Aist Go Jp Portals 0 Resource Images Aist J Aistinfo Aist Today Vol12 07 Vol12 07 P14 Pdf

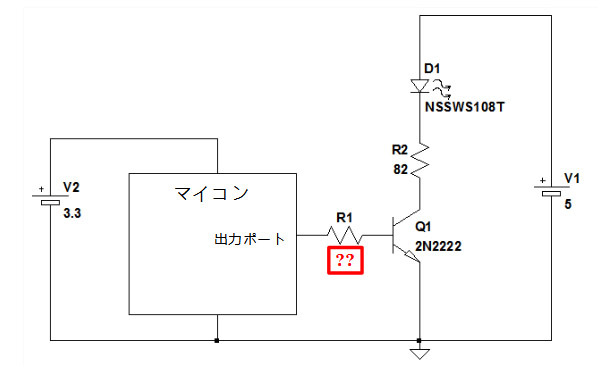

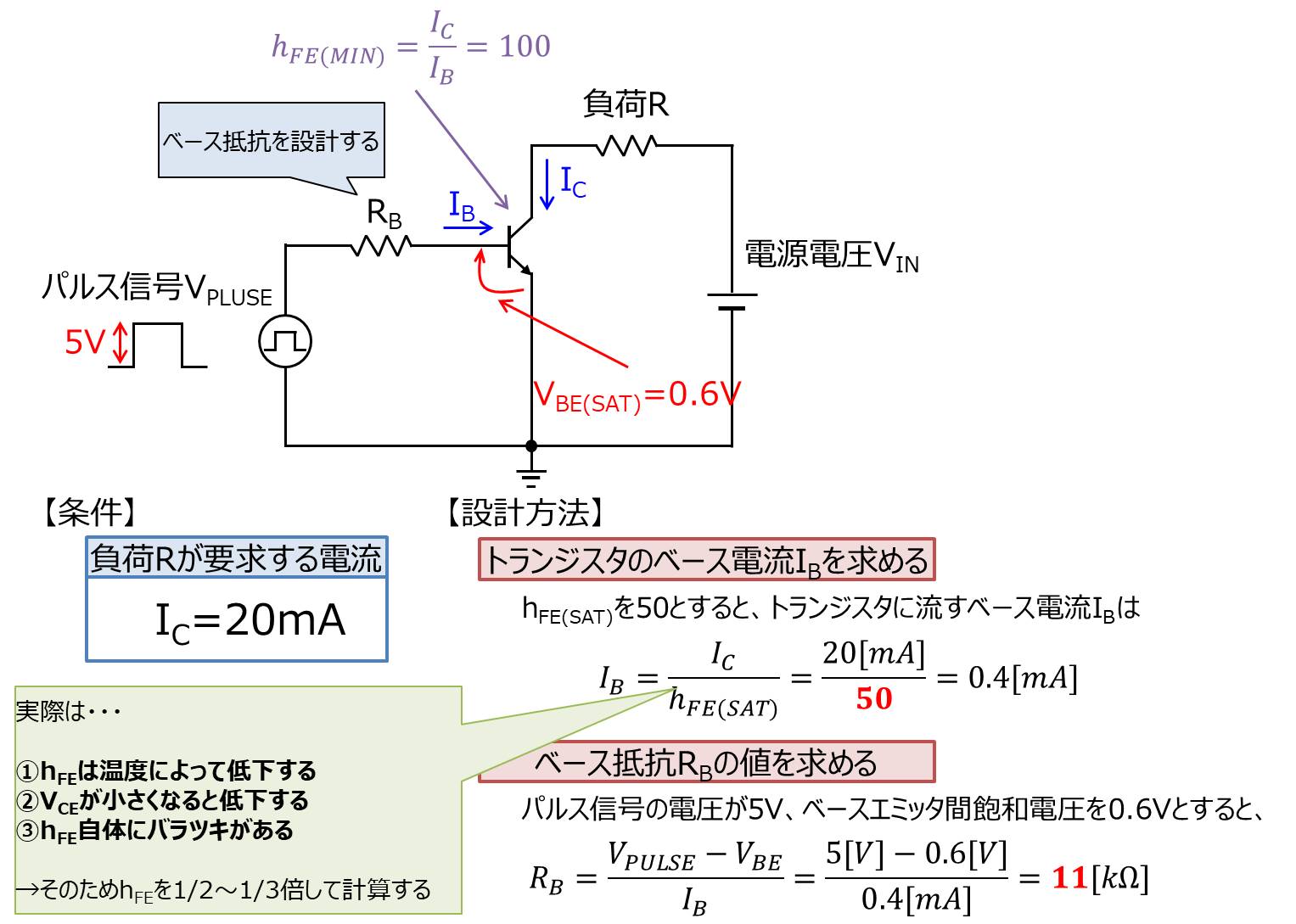

トランジスタのスイッチ回路で適切なベース抵抗は何w Cq出版社 オンライン サポート サイト Cq Connect

オペアンプについて 同相入力電圧範囲の 電源電圧特性 温度特性 ばらつきについて教えて下さい Faq Rohm Semiconductor

産総研 14 Nm世代立体型トランジスタの特性ばらつきの主要因を解明

産総研 特性ばらつきが小さい22 Nm世代フィントランジスタを作製

Mini Watters Project

Www Journal Ieice Org Conts Kaishi Wadainokiji 09 0906 Pdf

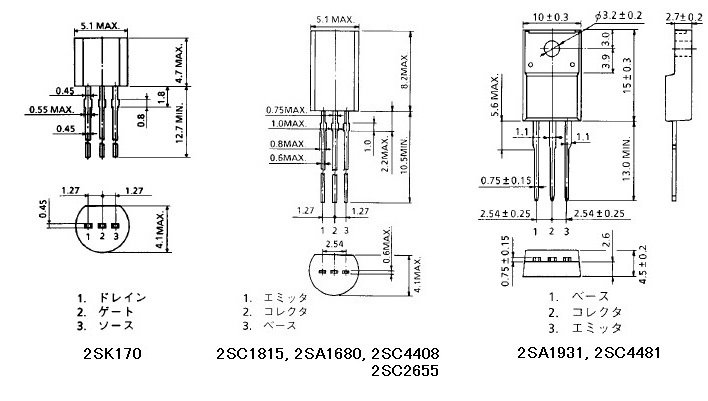

Fetの使い方 選定ガイド マルツオンライン

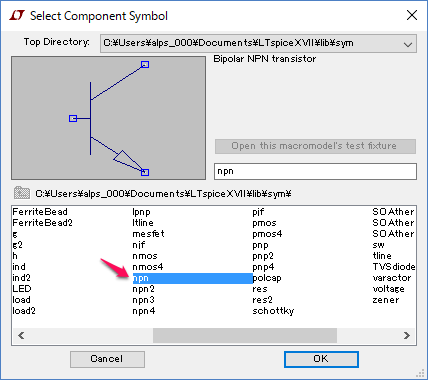

トランジスタの働きをltspiceで調べる 1 第1歩 Ltspice

産総研 特性ばらつきが世界最小のフィンfetを実現

アナログの基礎の基礎 トランジスタ編 5 バイポーラトランジスタ Venetor Sound

産総研 14 Nm世代立体型トランジスタの特性ばらつきの主要因を解明

産総研 14 Nm世代立体型トランジスタの特性ばらつきの主要因を解明

1998 号 定電流回路 Astamuse

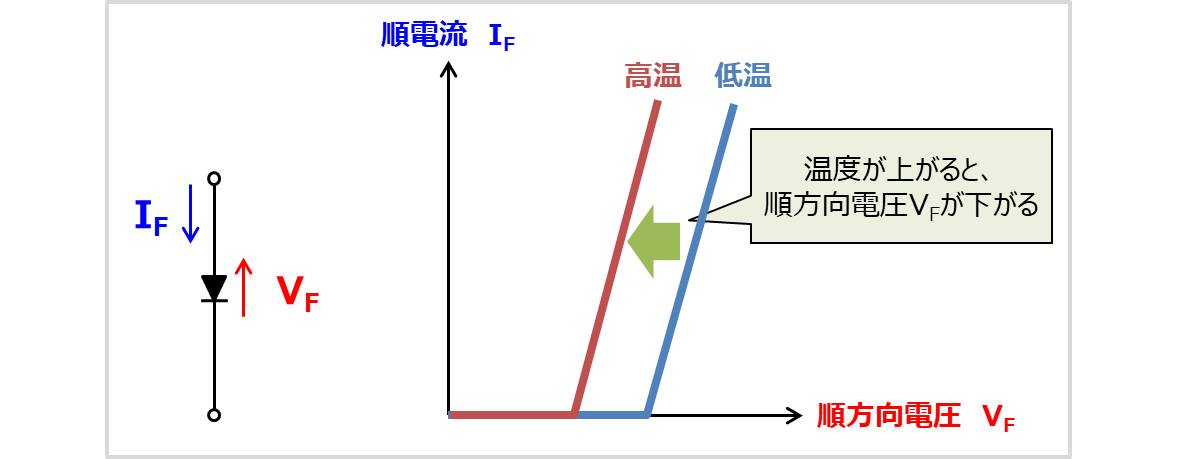

ダイオード 順方向電圧の温度特性について Electrical Information

Jpn Nec Com Techrep Journal G09 N01 Pdf Pdf

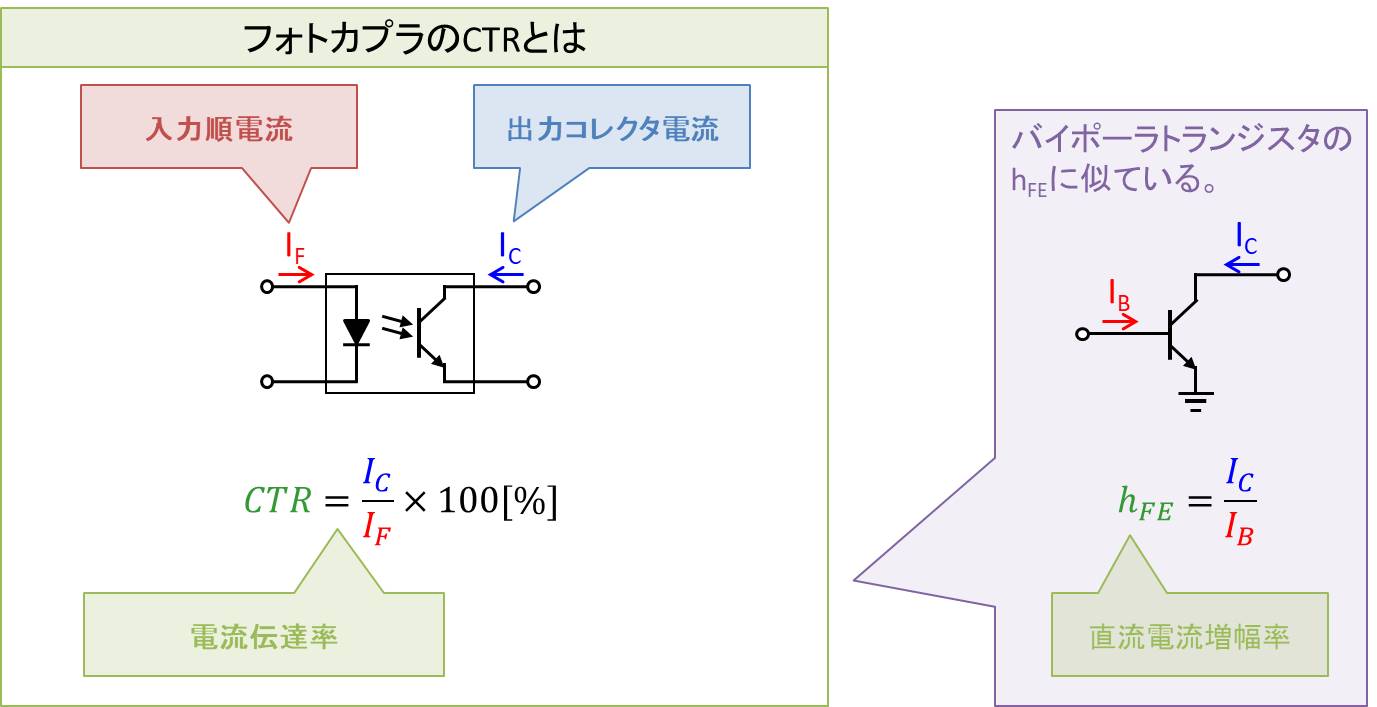

第7章 Tokyo Tech Ocw

10 号 ばらつきを考慮した半導体集積回路の設計方法 Astamuse

アナログの基礎の基礎 トランジスタ編 5 バイポーラトランジスタ Venetor Sound

03 号 集積回路におけるトランジスタ特性の合わせ込み方法 Astamuse

Leap Lsi消費電力削減のためmosの Vt低減 不揮発性メモリに力点 セミコンポータル

01 号 sigeベースバイポーラトランジスタ Astamuse

Ctrとは フォトカプラの電流伝達率について Electrical Information

研究内容

Bakoon Products 5 オフセット電流補正

半導体ばらつき設計解析技術 Naganoものづくり諏訪圏ガイド

株式会社ステラ コーポレーション

10 号 ばらつきを考慮した半導体集積回路の設計方法 Astamuse

東芝 研究開発センター 研究開発ライブラリ トランジスタの特性ばらつきを予測する3次元シミュレータ

トランジスタのhfe

第8回 エミッタ接地回路にばらつき対策施す 1 2 Ee Times Japan

Fetのランクのはなし Sudoteck

Ipsj Ixsq Nii Ac Jp Ej Action Repository Uri Item Id File Id 1 File No 1

半導体の各種先端技術紹介

Nmosトランジスタのばらつきは不純物だけでは決まらない セミコンポータル

Http Www Ieice Hbkb Org Files S2 S2gun 01hen 03 Pdf

産総研 フィン型トランジスタのばらつき要因を解決した新型sram回路の試作に成功

Cmosアナログのいまさらでも聞きたい Mosトランジスタの動作 18

10 号 ばらつきを考慮した半導体集積回路の設計方法 Astamuse

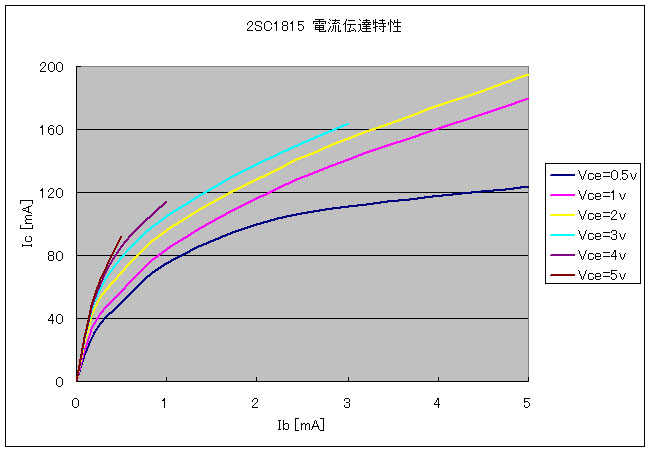

バイポーラトランジスタの 電流伝達特性 Ic Ib特性 について

Mosトランジスタのランダム バラつきの原因や対応策 Takeuchi Plot の竹内氏自身が講演 日経クロステック Xtech

こんなことを気にしてどうするの シリーズ 第4回 第5部 コーナー解析 The Sound Of Cadence Online Vol 17 日本ケイデンス デザイン システムズ

Http Www Nedo Go Jp Content Pdf

Nmosトランジスタのばらつきは不純物だけでは決まらない セミコンポータル

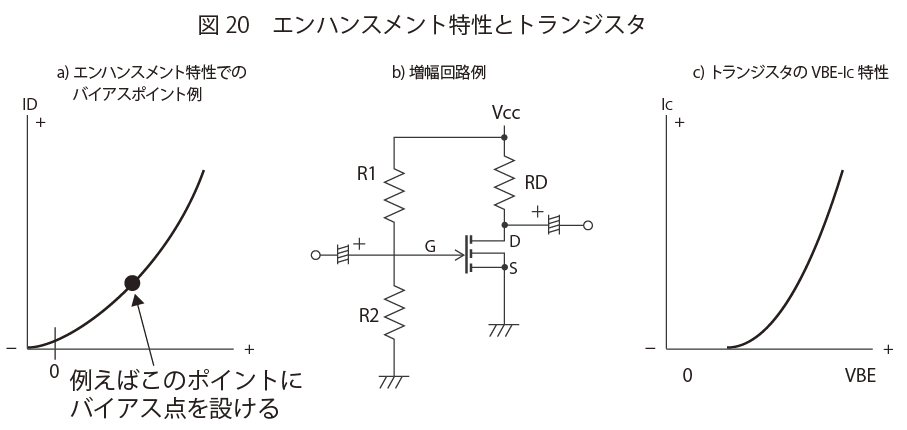

トランジスタのバイアス

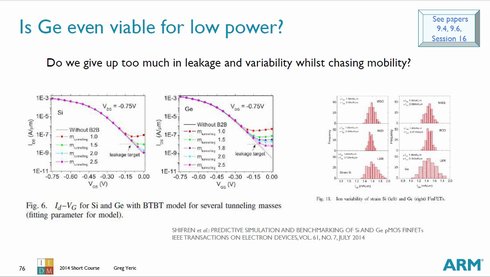

Armから見た7nm Cmos時代のcpu設計 13 高移動度finfetの期待と現実 2 2 Ee Times Japan

Http Semicon Jeita Or Jp Strj Strj 05 9f Ws05special Onodera Pdf

トランジスタのvbe

東芝 研究開発センター 研究開発ライブラリ 超低消費電力lsi向け ナノワイヤトランジスタにおける特性ばらつき低減

02 号 spiceトランジスタパラメータ抽出方法 Astamuse

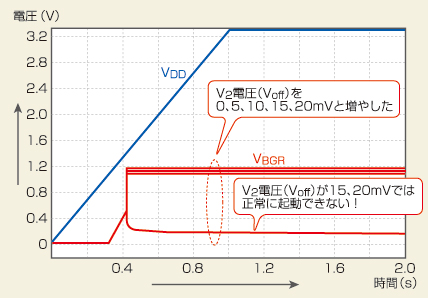

第36回 相対ばらつき も考慮してband Gap Referenceを設計 1 2 Ee Times Japan

05 号 差動増幅回路 Astamuse

産総研 14 Nm世代立体型トランジスタの特性ばらつきの主要因を解明

産総研 特性ばらつきが小さい22 Nm世代フィントランジスタを作製

こんなことを気にしてどうするの シリーズ 第4回 第5部 コーナー解析 The Sound Of Cadence Online Vol 17 日本ケイデンス デザイン システムズ

Http Www Am Ics Keio Ac Jp Digital Transistor Pdf

Http Www Am Ics Keio Ac Jp Digital Transistor Pdf

第13回 デジタル アシスト アナログ技術 その1 Edn Japan

2

トランジスタとは トランジスタのよくあるお問い合わせ エレクトロニクス豆知識 半導体のローム Rohm

Cmosアナログのいまさらでも聞きたい Mos特性等

等価回路について

Http Semicon Jeita Or Jp Strj Strj 05 9f Ws05special Onodera Pdf

Ipsj Ixsq Nii Ac Jp Ej Action Repository Action Common Download Item Id Item No 1 Attribute Id 1 File No 1

Cmosアナログのいまさらでも聞きたい Mos特性等

デジタルトランジスタ デジトラ の原理 トランジスタとは エレクトロニクス豆知識 ローム株式会社 Rohm Semiconductor

1 デバイス特性ばらつきの評価 Pdf 無料ダウンロード

デジタルトランジスタ デジトラ の原理 トランジスタとは エレクトロニクス豆知識 ローム株式会社 Rohm Semiconductor

微細化に堪え得るオンチップsram 1 3 Edn Japan

02 号 spiceトランジスタパラメータ抽出方法 Astamuse

ベース抵抗 と ベースエミッタ間抵抗 の役割 なんで付いているの Electrical Information

情報技術の心臓部として活躍するlsi その設計課題に挑戦 研究室voice 大阪工業大学

トランジスタの電流増幅率を制御する 応答特性 その他の例 An Engineer19のブログ

08 1123号 半導体集積回路設計方法 および設計プログラム Astamuse

10 号 ばらつきを考慮した半導体集積回路の設計方法 Astamuse

Finfetのアナログ適用 デジタル回路が不可欠 日経クロステック Xtech

pnp trによるマルチバイブレータ

Cmosアナログのいまさらでも聞きたい Mos特性等